# **SYNOPSYS**<sup>®</sup>

## QuickCap NX 3D Field Solver

QuickCap NX is the gold standard 3D Field Solver solution for advanced process technologies down to 3nm with FinFET, nanosheet, and vertical FET device architectures

### Overview

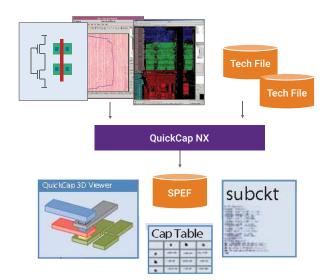

QuickCap® NX is a high-accuracy 3D parasitic field solver for foundry process technology development and circuit analysis. QuickCap NX includes key capabilities that address critical design challenges that occur in FinFET, nanosheet, and vertical FET process technologies down to 3nm. QuickCap NX is also used by foundries for modeling complex middle-of-line (MEOL) parasitic effects which have become more prominent at advanced process geometries. With its advanced process modeling features, a parallel execution mode and reference-level SPICE netlist generation and reduction capabilities, users can shorten the development cycle by more accurately predicting silicon performance.

- Field solver solution for early process technology node exploration and parasitic modeling development

- Advanced random-walk algorithm offers self-capacitance, coupling capacitance and distributed capacitance extraction for test structures and critical nets

- Supports detailed process modeling of complex geometries and process effects for accurate analysis of device and interconnect parasitics

- Used by Foundries for high-accuracy 3D modeling using uniquely detailed silicon profiles

- 3D graphical viewer allows visibility into the exact process profile being modeled

- Faster runtime enabled by multicore processing, tiling, bounded nets and hierarchical extraction for increased designer productivity

Figure 1: QuickCap NX 3D field solver solution enables early process exploration and characterization

As geometries shrink and clock frequencies increase, designers need more accurate parasitic values to reduce risk of design failure. The growing need for more accuracy makes it necessary to account for precise fringing electrostatic fields and process effects in test structures and analyzing critical cells, blocks, and nets. QuickCap NX provides robust, consistent, and accurate 3D capacitance extraction with capacity to handle moderately sized blocks or long critical nets. QuickCap NX's proven modeling capabilities allow users to perform accurate noise and timing analysis for robust design development and improved silicon success.

#### Advanced 3D Modeling and Process Development

QuickCap NX includes the ability to create 3-D physical models which precisely match advanced process technology profiles and account for new effects like, diamond EPI growth, EPI and trench contact parasitics, and non-linear gate resistance. The unique capability allows foundries and early technology adopters to engage earlier to explore device parasitic capacitance effects in new technology nodes and accelerate the development schedules.

An exclusive technology file encryption feature provides foundries with a secure method of sharing critical process information with their customers, allowing them to enhance the accuracy of their analysis and speedup the migration to new nodes. In addition, multicore capabilities and hierarchical processing significantly improve runtime, and a powerful 3D graphics viewer simplifies the development and debug of new complex circuit structures and technology files. As a result, QuickCap NX is broadly used in process studies, characterization and correlation across several generations of process nodes, and to support highly accurate device-level SPICE simulations.

#### Modeling down to 3nm

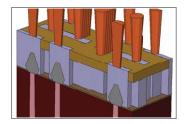

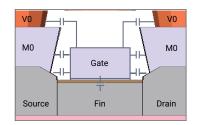

FinFET, nanosheet, and vertical FET process technologies achieve better control over the source-drain channel because the gate encloses the channel on three or more sides, resulting in higher mobility, greater drive strength, lower switching currents, and lower leakage currents. This 3D architecture also introduces more complex geometries and many new capacitive elements that require highly accurate modeling. QuickCap NX's geometry pre-processing engine provides a highly accurate physical profile of the FinFET, nanosheet, or vertical FET for modeling, and its graphical viewer allows users to see exactly how the device will be modeled. Finally, the core 3-D field-solver engine of QuickCap NX accurately extracts the capacitance values from the model. Combined, these capabilities allow QuickCap NX to provide the necessary precision to model devices down to 3nm and as a result it has been adopted by leading foundries for this purpose.

#### Powerful Geometry Processing Engine

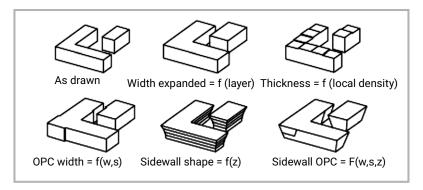

The geometry pre-processor capability "gds2cap" translates the 2D layout data into a 3D representation and reduced SPICE netlist with resistance and capacitance. The gds2cap capability includes a flexible polygon-processing engine that handles multiple conformal dielectrics, non-Manhattan geometries, non-planar metals, metal fill, process effects (OPC, CMP, Trapezoidal wire), device recognition, resistance extraction and exclusion of device capacitances. QuickCap NX takes the 3D representation and the netlist output from the gds2cap interface, produces an output file containing self and coupling- capacitance values and replaces the capacitance values in the netlist with accurately computed values from QuickCap NX.

Detailed Silicon Profile based 3D Modeling

Accurate Middle-of-line Parasitic Extraction

Figure 2: QuickCap NX is used by foundries for FinFET modeling down to 5nm

Figure 3: QuickCap NX provides precise physical models of process effects

#### Proven Parasitic Capacitance Extraction

QuickCap NX has demonstrated close correlation to silicon measurements at various process nodes. Its advanced modeling, including modeling of optical, copper, Ruthenium, and new conducting material effects as well as in-die process variations, enable increased accuracy. The validation of QuickCap NX's silicon accuracy by foundries has led to its wide use in early process technology development and device characterization.

For advanced users, QuickCap NX also provides a dial-in accuracy and error- bounds reporting on each net, providing the flexibility and control for their target application needs.

#### Handling Large Layouts

QuickCap NX provides multiple techniques to enable critical net analysis in designs too large to fit in memory. Runtime or memory use can be reduced by using tiling, bounded nets, hierarchical processing, multicore processing or a combination of these techniques.

#### **Key Features Summary**

- · 3D modeling of FinFET, nanosheet, and vertical FET process technologies down to 3nm

- · Accurate extraction of self-coupling and distributed capacitance

- Robust and accurate handling of complex geometries including non-Manhattan structures, conformal dielectrics, and floating metal

- · Advanced process effects for in-dieprocess variation, optical, copper, Ruthenium, and new conducting material effects

- 3D graphics viewer

- · Dial-in accuracy and error bounds reporting for each net

- · Low memory usage independent of accuracy

- Runtime independent of net length

- · Exclusion of device capacitance and optional inclusion of device fringe capacitance

- Parasitic reduction

- · Flat and hierarchical processing

- Tile or bounded net analysis

- Multicore processing

- Technology file encryption

#### Input

- · GDSII or scripted text

- Output

- Back annotated SPICE netlist

- · Capacitance summary in a matrix

- Platform/OS

- 64 bit Solaris and Linux

For more information about Synopsys products, support services or training, visit us on the web at: <u>www.synopsys.com</u>, contact your local sales representative or call 650.584.5000.